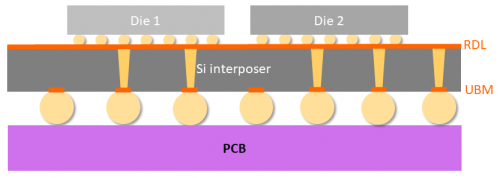

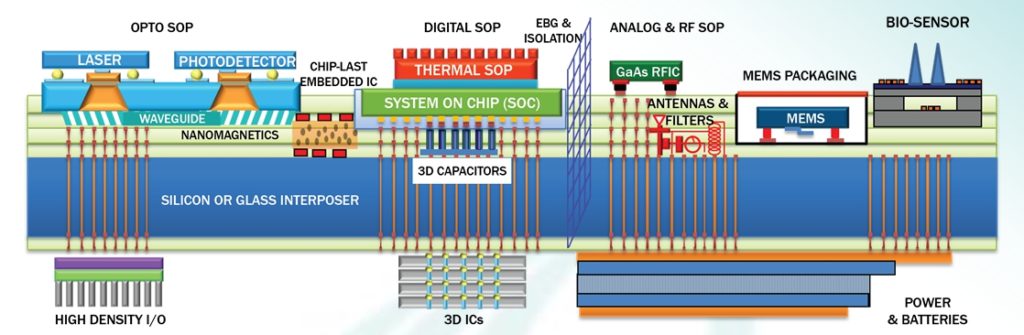

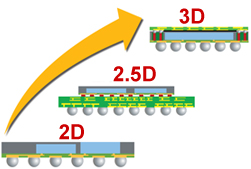

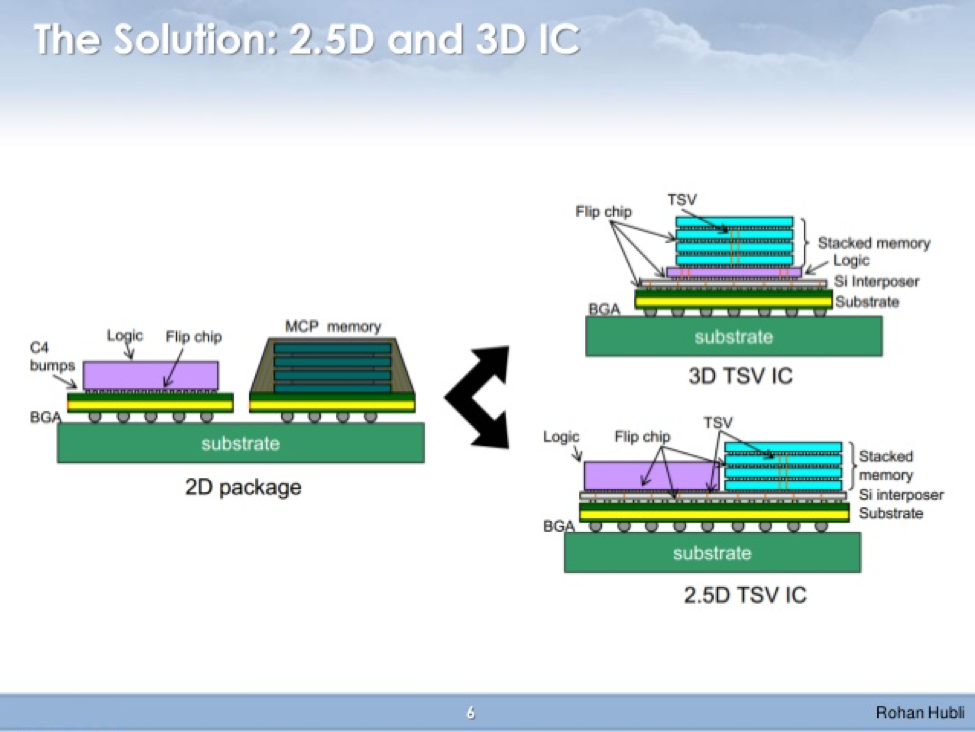

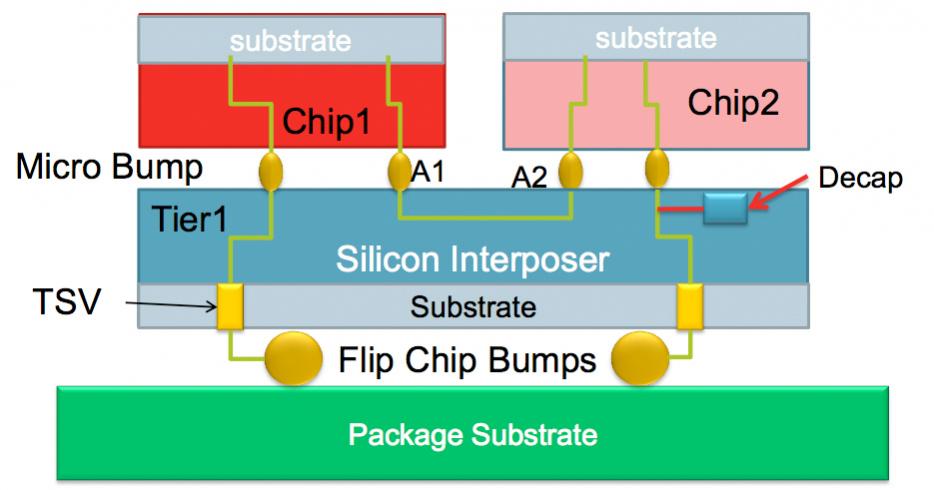

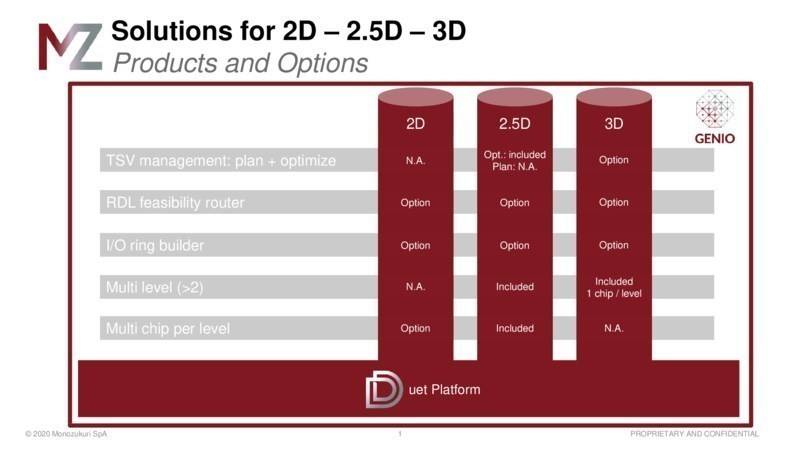

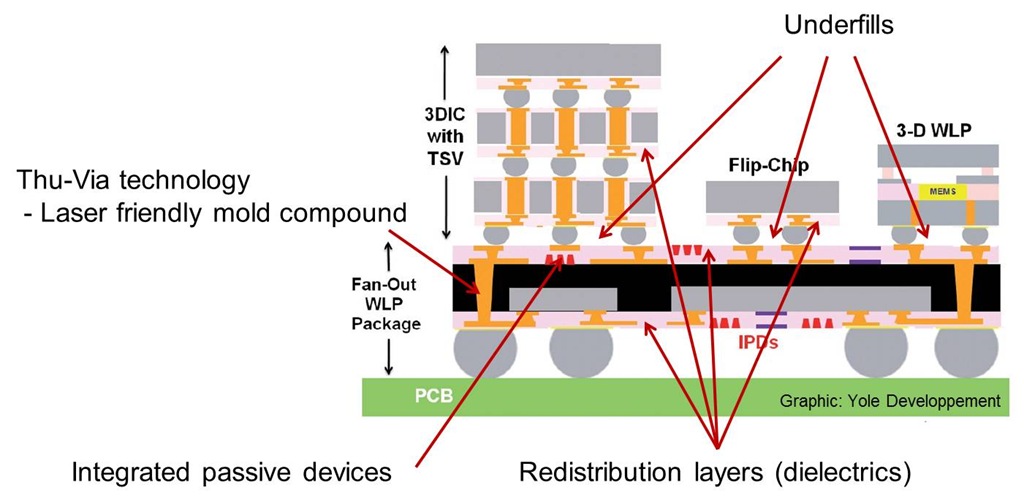

Synopsys introduced its 3DIC Compiler platform to transform the design and integration of complex 25 and 3D multidie system in a package It provides an unprecedented fully integrated, highperformance, and easytouse environment, offering architectural exploration, design, implementation, and signoff with signal, power, and thermal integrity optimizations, all inFig 1, which shows a modern 25D test vehicle including packaging technologies such as silicon interposer and micropillar interconnects 3 Figure 1 shows two fullwaferthickness dice, which are stacked on a thinned silicon interposer The dice package is25D (twoandahalf dimensional, alternatively pseudo3D or threequarter) perspective refers to one of two things Gameplay or movement in a video game or virtual reality environment that is restricted to a twodimensional (2D) plane with little to no access to a third dimension in a space that otherwise appears to be threedimensional;

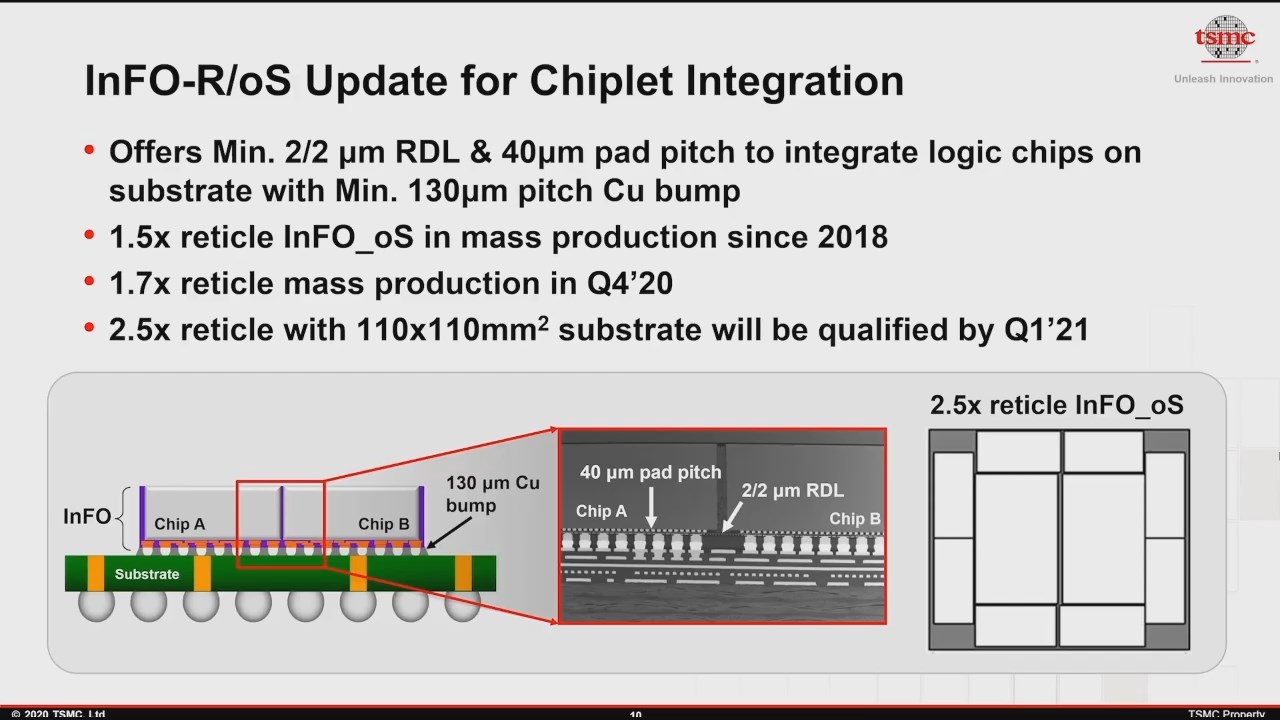

Highlights Of The Tsmc Technology Symposium 21 Packaging Semiwiki

2.5 3d packaging

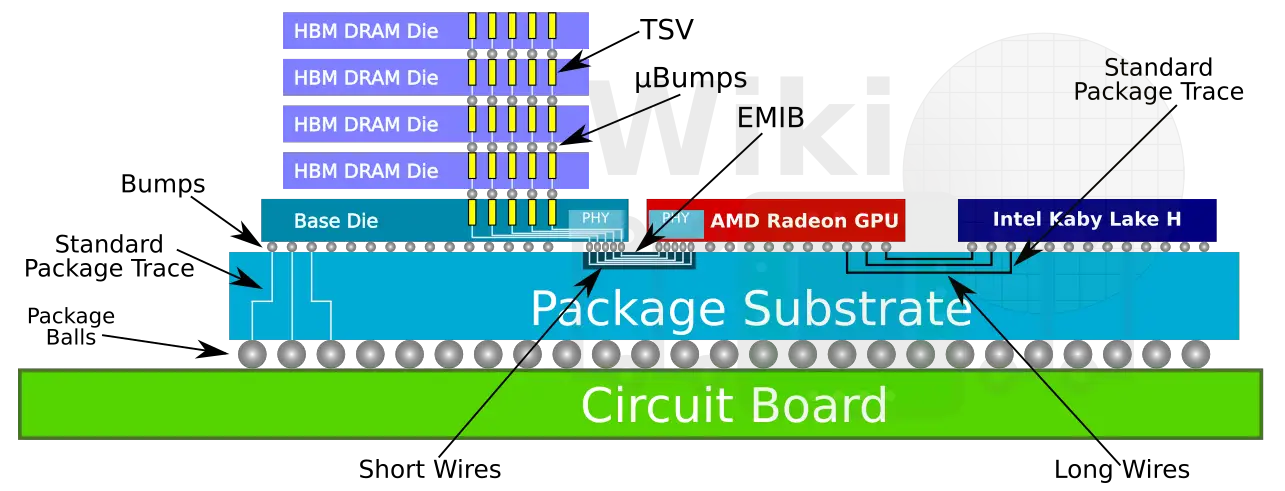

2.5 3d packaging- AMD GPU VEGA Product 25D/3D Package with HBM2 • AMD GPU Vera Package Supply Chain • GLOBALFOUNDRIES GPU and interposer • ASE Assembly • Samsung HBM2 • IBIDEN laminate subtrate TSV inside HBM and Silicon Interposer •Heterogeneous and homogeneous 25/3D IC package connectivity planning and prototyping for system technology cooptimization Full or Partial Schematics Import Package assembly logical connectivity can be constructed by using full or partial graphical schematics, useful for high device count designs such as SiP modules and/or the reuse

Advanced Packaging Osats Foundries And Idms Part Of The Game

Lower density 25D/3D package architectures, 1050 μm diameter, aspect ratio of 41 to 61 and μm pitch;Use the model to for your product Include supplier specific details and incoming die preparation in your analysis View the detailed costs—including labor, material, capital, tooling, and yield impacts—for every step Labor rate Lot size Overhead rate Most experts believe that full 3D packaging is at least five years away from mainstream deployment 25D, in contrast, already has made inroads in markets where price sensitivity is low and demand for throughput to memory is extremely high, such as networking, server and graphics applications

Close mobile search navigation Article navigation Volume 13, Issue 12D graphical projections and similar techniques 2D vs 25D vs 3D ICs 101 By Max Maxfield 6 I see a lot of articles bouncing around the Internet these days about 25D and 3D ICs One really good one that came out recently was 25D ICs are more than a stepping stone to 3D ICs by Mike Santarini of Xilinx On the other hand, there are a lot of other articles that have "3D ICs

David Schor 25D packaging, 3D packaging, CoEMIB, EMIB, Foveros, Intel A look at ODI, a new family of packaging interconnect technologies that bridges the gap between Intel's EMIB (25D) and Foveros (3D) by providing the flexibility of an EMIB in 3D with additional benefits of thermal & powerSignoff Verification of 25/3D Stacked Die Assemblies Provides complete design verification of stacked die assemblies Delivers 3D assembly LVS for assemblies such as stacked memories, stacked sensor arrays, interposerbased structures, or packagelevel RDL routing25D packaging using silicon interposers with TSVs is an incremental step toward 3D packaging

Http Www Mouser Be Pdfdocs Ipdia Wp Silicon interposers Pdf

Figure 1 From 2 5d 3d Tsv Processes Development And Assembly Packaging Technology Semantic Scholar

25/3D Level Heterogeneous Integration • Heterogeneous Integration • In the context of describing 25D/3D packaging level of technology • Integrating dissimilar chips using a packaging technology with I/O density higher than organic substrate (Feature size smaller than organic substrate, or 3D die) • Technology drivers • High bandwidthSome sophisticated 25D assemblies even incorporate TSVs and 3D components Several foundries now support 25D packaging 6 7 8 9 10 The success of 25D assembly has given rise to "chiplets" – small, functional circuit blocks designed to be combined in25D & 3D Packaging Indium Corporation is a world leader in the design, formulation, manufacture and supply of semiconductorgrade fluxes and associated materials, enabling 25 and 3D assembly processes, as well as more standard flipchip assembly

2 5d 3d Ase Group

Rolfsted If Dk Hp Ssd S700 Pro 2 5 256gb Sata Iii 3d Nand Internal Ssd 2ap98aa Abl Drives Storage Blank Media Computers Tablets Networking

Vias can be filled or barrel coated;Figure 1 illustrates 25/3D stack packaging trends from those that are in the development stage to those that are now mainstream The 25D covers segmented die with passive TSV interposer within package or active interposer with packages, also known as system in a package (SiP) The 3D packaging consists of stacking25/3D HI Packaging – Foundation and Future Vision Author Douglas J Sheldon Subject 21 NEPPETW Presentation Created Date AM

Design Electrical Mechanical Thermal Prc Gatech Edu Georgia Institute Of Technology Atlanta Ga

1

25/3D IC Package Planning Early prototyping and exploration allows engineers to evaluate different ASIC/chiplet, interposer, package, and PCB integration scenarios in order to meet overall PPA, device size, routability, and cost goals prior to detailed physical implementation Samsung Foundry Certifies Cadence System Analysis and Advanced Packaging Design Tool Flow for 25/3D Chip Designs Proven flow featuring the Celsius Thermal Solver and Clarity 3D Solver accelerates 25/3D designs for hyperscale, communications and 1325D/3D TSV & Wafer Level Integration Technology & Market updates 19 Sample wwwyolefr ©19 In this report ADVANCED PACKAGING PLATFORMS Focus on 3D stacking packaging platforms in this report No substrate FanOut WLCSP Organic substrates Wirebond BGA CSP COB BOC WB CSP LGA FlipChip BGA FC BGA FO on Substrate 25/21D 3D*

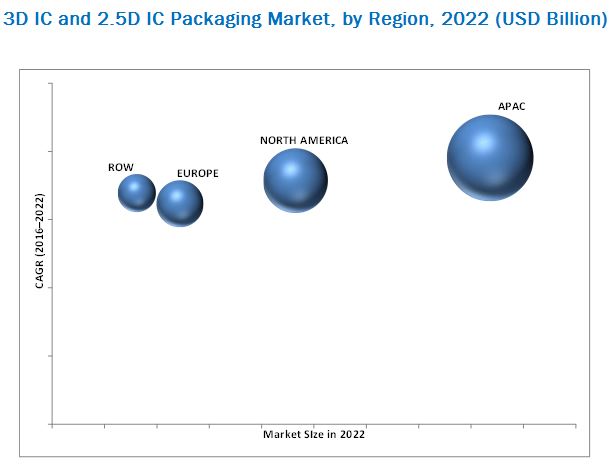

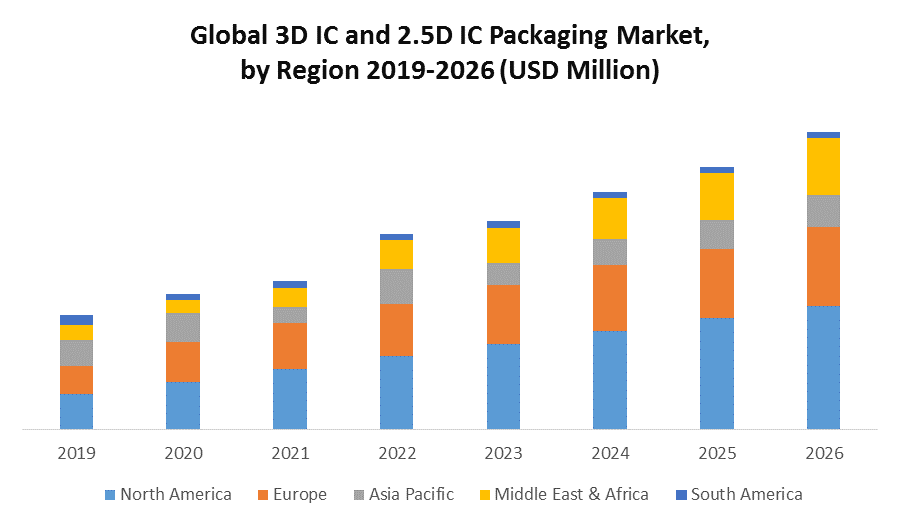

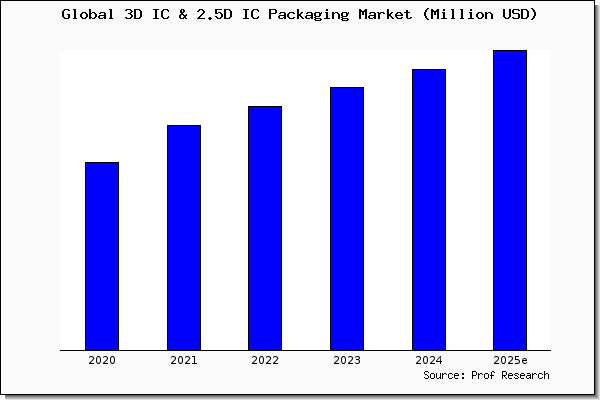

3d Ic And 2 5d Ic Packaging Market Global Industry Analysis Trends Market Size And Forecasts Up To 24

Plasma Etch And Deposition Solutions For 2 5d 3d Packaging Spts

Many small dies are packaged in parallel for high performance needs • Datacenter bandwidth and performance needs are driving photonic packaging Application Package Types Data Center • Large 25D packages with HBM and ASIC w/ 3D SRAM Samsung Foundry Certifies Cadence System Analysis and Advanced Packaging Design Tool Flow for 25/3D Chip Designs Proven flow featuring the Celsius Thermal Solver and Clarity 3D Solver accelerates 25/3D designs for hyperscale, communications and25D is a packaging methodology for including multiple die inside the same package The approach typically has been used for applications where performance and low power are critical Communication between chips is accomplished using either a silicon or organic interposer, typically a chip or layer with throughsilicon vias for communication While communication between chips

High End Performance Packaging 3d 2 5d Integration I Micronews

3d Ic And 2 5d Ic Packaging Market Size Share Trends Analysis Industry Report 24 Igr

25/3D wafer level packaging is one of the important key technologies in advanced microelectronic packaging and system integration worldwide This concept has specific advantages in terms of heterogeneous integration of multiple devices such as sensors, processors, memory ICs and transceivers with excellent electrical performance and small form factor This study explored Through Glass Via (TGV) Formation Technology by using Focused Electrical Discharging Method for alkalifee glass which has well matched CTE with Si 25D/3D Packaging has presently attracted lots of attention, an interposer is recognized as one of key materials, and its development of new fine pitch, high dense, and low cost interposer arePower & Signal integrity prototyping in system technology cooptimization (STCO) High Density Advanced Packaging (HDAP) using chiplets & 3D packaging Using a System Technology CoOptimization (STCO) approach for 25/3D Heterogeneous Semiconductor Integration

Conventional Process Flow For 2 5d 3d Ic Integration Chip On Download Scientific Diagram

3d Packaging Breaking New Ground Yole Pradeep S Techpoints

25D/3D packaging I've spent most of my career in the ASIC business In 03, Gartner predicted the ASIC market would grow to $169B During that time, there were a number of startups building ASICs, but the applications were a bit specialized and aimed at new marketsSelect a packaging style, quantity, and choose from custom or stock sizes – then start designing your custom boxes Add customization options like images, text, and any color your brand requires As you design you'll see an instant quote so you know exactly what your final order will come to Get started now Tiny minimums IFTLE 461 Samsung 3DIC XCube;

Different 3d Technologies Arranged According To Manufacturing Costs And Download Scientific Diagram

3d Ic And 2 5d Ic Packaging Market By Application Logic Imaging 22 Marketsandmarkets

25D And 3DIC LatchUp Prevention 25D/3D ICs have evolved into an innovative solution for many design and integration situations, but they present unique verification obstacles that challenge electronic design automation (EDA) tools originally designed for 2D ICs Automated solutions are needed not only to reduce verification cycles but also• Scalable compute packaging is an emerging trend – Single small die is used for low end needs; 25/3D IC Packaging Technologies Part 1 Overview IEEE/CPMT, Herb Reiter eda2asic Consulting IncHerb Reiter, eda2asic Consulting, Inc herb@eda2asiccom 1 eda2asic AGENDA Part 1 Introduction eda2asic EndUseMarkets for 25/3D

3d Ic And 2 5d Ic Packaging Market Constraints And Growth Strategies 29 Saudi 24 News

Eps Ieee Org Images Files Hir 19 Hir1 Ch22 2d 3d Pdf

Packaging should be the same as what is found in a retail store, unless the item is handmade or was packaged by the manufacturer in nonretail packaging, such as an unprinted box or plastic bag item 4 Western Digital WD Blue 25" 3D NAND SATA SSD Solid State Drive 1TB **NEW** 4 Western Digital WD Blue 25" 3D NAND SATA SSD SolidHuemoeller , " Market Demand Readiness for 2 5 / 3 D TSV Products " IMAPS 12 Device Packaging Conference , Scottsdale , AZ March 5 12 2 S Arkalgud , " 2 5 and 3 D• 25/3D packaging process and materials are more sophisticated than in the traditional flip chip packaging technology o The industry mainstream SoA 25/3D package assembly process, materials, and business model are not currently compatible with low volume production for mil/space components

Advanced Packaging Strong Momentum Driven By Tsmc Intel And Samsung Ee Times Asia

Conventional Process Flow For 2 5d 3d Ic Integration Chip On Download Scientific Diagram

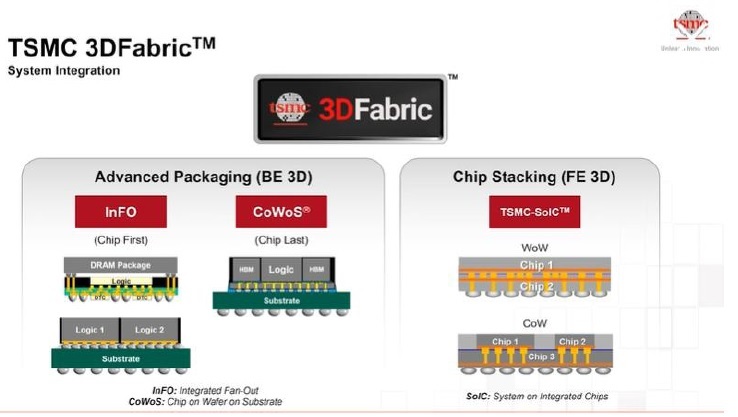

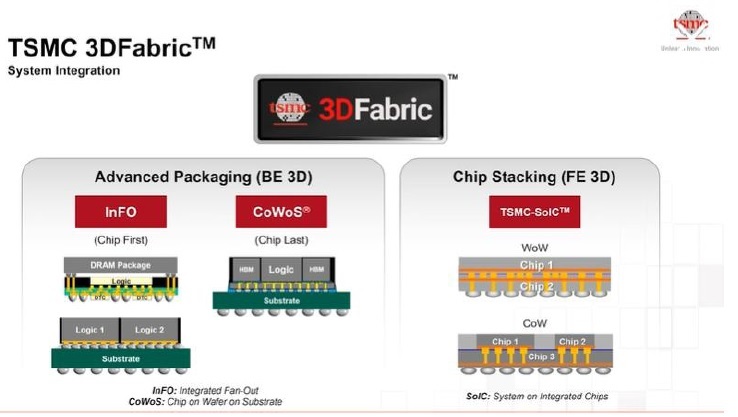

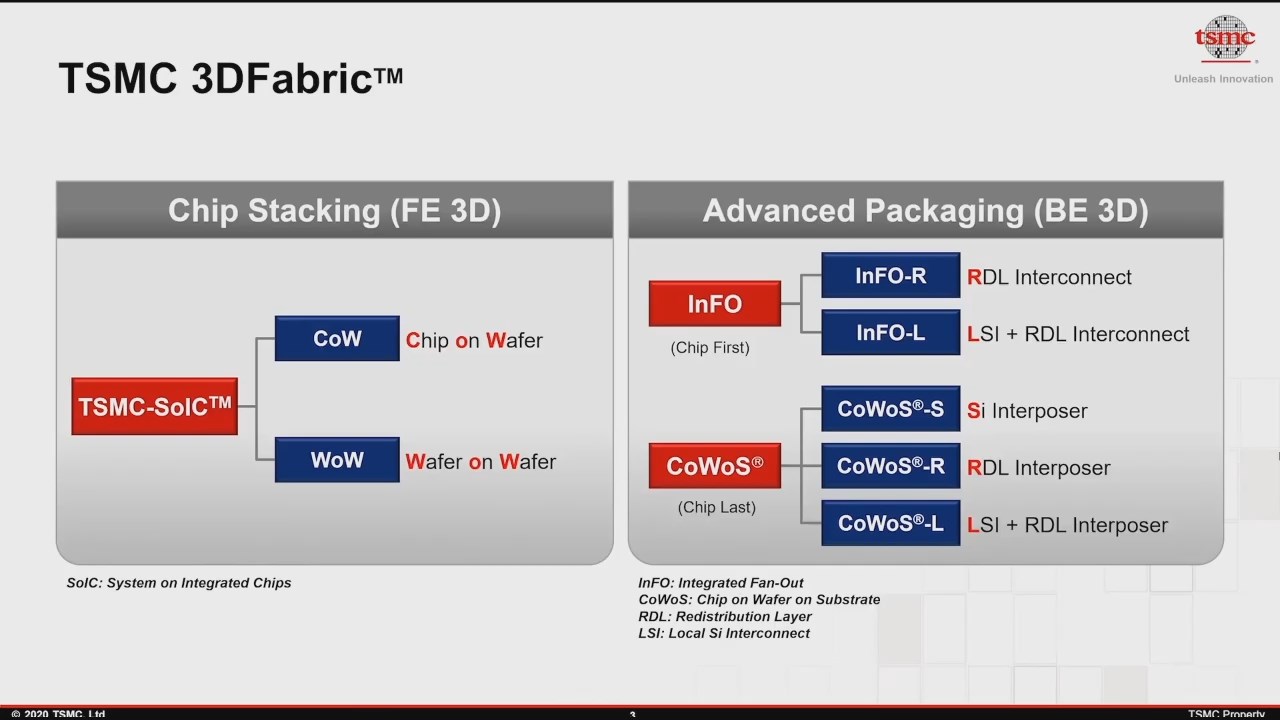

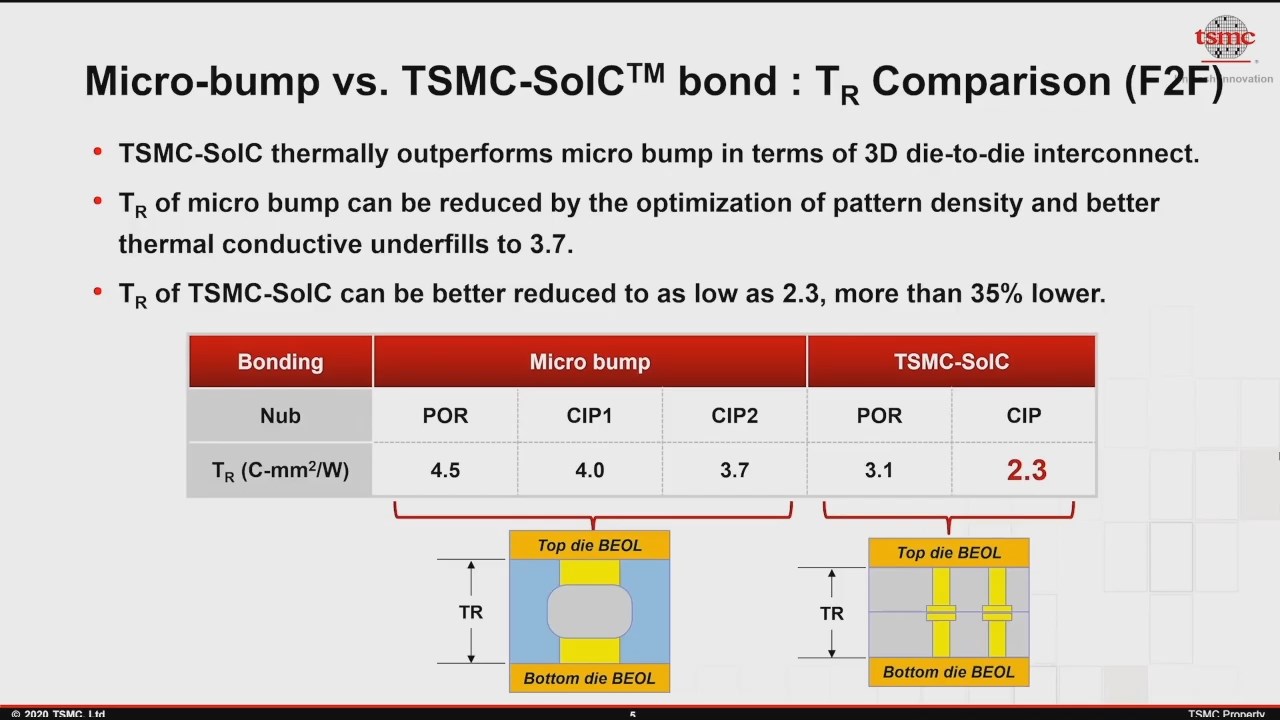

Automated verification of 25/3D IC latchup prevention With the Calibre PERC reliability platform, an automated 25/3D IC latchup prevention verification methodology is available that addresses the multiple challenges inherent in advanced latchup protection for multidie packages In order to unify all the different names it gives to its variants of its 25D and 3D packaging, TSMC has introduced its new overriding brand 3DFabric 3DFabric makes sense as a brand to tie the 25D/3D packaging technologies are revitalizing creativity in high technology products We thought we knew what faster, better, lighter and smaller meant 25D/3D packaging can revolutionize what we thought possible but it will require augmenting our current methods and tools One key methodology to add would be Path Finding

3d Ic And 2 5d Ic Packaging Market By Application Logic Imaging 22 Marketsandmarkets

2 5d 3d Ic Market Challenges Opportunities

25D & 3D Packaging Cost Model Which applications are right for this technology?Comprehensive 25/3D IC packaging design solution for heterogeneous IC/chiplet integration that utilizes a STCO IC packaging process methodology25/3D IC Package Thermal Modeling Modeling heterogeneous 25/3D ICpackage thermal chippackageinteractions is important for several reasons Designing a large high power device, eg a AI or HPC processor without considering how to get the heat out is likely to lead to problems later on, resulting in a suboptimal packaging solution from

Webinar Design Methodologies For Next Generation Heterogeneously Integrated 2 5 3d Ic Designs Semiwiki

Eng Sub 2 5d Package Technology Gpu Hbm Amd Nvidia Tsmc

#2 In general, 3D packaging's processing feature sizes are huge (in microns vs in nanometers in actual leading edge logic devices) So ASML does not play a role in this space (or at least EUV is not needed, and will never be needed) Instead, lithography equipment handling bigger features but with higher productivity, like fromWafer thinning (to < μm Si thickness) and processing on temporary carrier waferIntel Announces Hybrid Bonding By Phil Garrou Blogs Samsung's XCube Samsung has announced that its advanced 3D integrated circuit (IC) packaging technology, dubbed "XCube," is now available for

Advanced Packaging Market To Grow 8 To 26 10 07 Packaging Strategies

Advanced Packaging Strong Momentum Driven By Tsmc Intel And Samsung Ee Times Asia

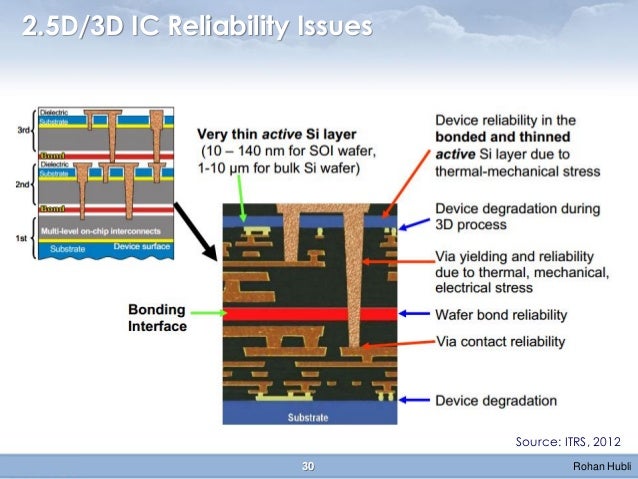

25/3D packages (Quasi) monolithic integration (System in Package or SIP) is an ongoing trend to increase functionality and reduce cost This includes technologies such as the integration of multiple active and passive (prepackaged) components into one overmold package, diestacking and package stackingTogether with 25D/3D packaging this extends Moore's Law at systemlevel Times have changed The industry is seeking alternatives to design and manufacture the latest Systems on Chips (SoCs) using System in Package (SiP) and chipletbased approaches by leveraging HighEnd Packaging to mix both the latest and mature nodes 25D/3D packaging Threedimensional (3D) packaging with throughsiliconvias (TSVs) is an emerging technology featuring smaller package size, higher interconnection density, and better performance;

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Pin On Telecharger Gratuit

High density 3D IC applications, filled 210 μm diameter, up to 81 aspect ratio and 1050 μm pitch; 3D is an overused term that means different things to different people Some call 25D a 3D technology Technically, a DRAM stack, which has been wirebonded, is also 3D "Traditionally, 3DIC means something with a throughsilicon via through an active die People are taking that in different directions," ASE's Rice explained

Http Ewh Ieee Org Soc Cpmt Presentations Cpmt1404a Pdf

3d Ic And 2 5d Ic Market By Packaging Technology 3d Tsv 3d Wafer Level Chip Scale Packaging 2 5d Application Imaging Optoelectronics Logic

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Eetimes 3d Ic Design

2 5d 3d Ase Group

Russia 3d Ic And 2 5d Ic Packaging Market Prospects Trends Analysis Market Size And Forecasts Up To 24

More 2 5d 3d Fan Out Packages Ahead

Advanced Packaging Five Trends To Watch In 17 Electronic Products

Www Circuitinsight Com Pdf 2 5d 3d Semiconductor Package Technology Ipc Pdf

3d Ic And 2 5d Ic Packaging Market In Depth Analysis Taiwan

Concept Of A 2 5 D System In Package With Active Lite Interposer And Download Scientific Diagram

Intel Looks To Advanced 3d Packaging For More Than Moore To Supplement 10 And 7 Nanometer Nodes Page 2 Wikichip Fuse

Yole Yole Developpement Yole Developpement Yole Development System Plus System Plus Consulting Piezoelectric Bulk Bulk To Thin Film Thin Film Piezo Sensors Actuators Transducers Mobile And Consumer Automotive And Transportation Defense

Global 3d Ic And 2 5d Ic Packaging Market Industry Analysis

Http Www Cetimes Com Sip 18 Download 1 Sp 2 Pdf

Malaysia 3d Ic 2 5d Ic Packaging Market

Http Ewh Ieee Org Soc Cpmt Presentations Cpmt1105a Pdf

2 5d Packaging Wikichip Fuse

2 5 3d Packaging Path Finding 3d Incites

What Is 3d Integration 3d Incites

Yole Yole Developpement Yole Developpement Yole Development System Plus System Plus Consulting Piezoelectric Bulk Bulk To Thin Film Thin Film Piezo Sensors Actuators Transducers Mobile And Consumer Automotive And Transportation Defense

2 5d And 3d Ics New Paradigms In Asic Product Engineering Blog Einfochips

1

Iftle 468 Samsung Advanced Packaging At The Virtual Iwlpc 3d Incites

Packaing Part 4 2 5d And 3d

High End Performance Packaging 3d 2 5d Integration I Micronews

Advanced Packaging Osats Foundries And Idms Part Of The Game

About 2 5d Technology Nhanced Semiconductors Inc

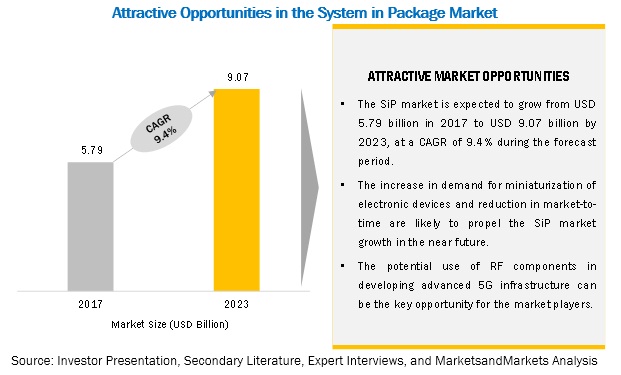

System In Package Market By Packaging Technology Package Packaging Method Device Application Covid 19 Impact Analysis Marketsandmarkets

2 5d Semiconductor Engineering

2 5d 3d Ic Market Challenges Opportunities

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

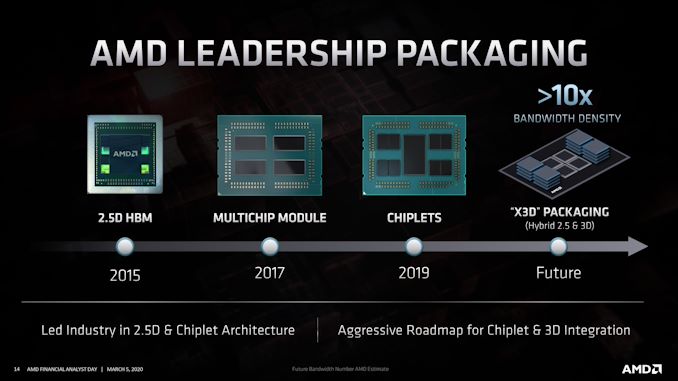

Amd Discusses X3d Die Stacking And Packaging For Future Products Hybrid 2 5d And 3d

Nepp Nasa Gov Workshops Etw18 Talks 19june18 1330a sheldon nepp etw djs final Pdf

Outlook For 3d And 2 5d Chips In Smartphones

2 5d And 3d Ics New Paradigms In Asic Product Engineering Blog Einfochips

Figure 3 1 From Microelectronics Packaging Technology Roadmaps Assembly Reliability And Prognostics Semantic Scholar

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Jcet Group 2 5d 3d Integration

Intel Leans Hard On Advanced Chip Packaging Technologies In Battle For Computing Supremacy Venturebeat

3d Ic And 2 5 D Ic Packaging Industries In Depth Analysis

More 2 5d 3d Fan Out Packages Ahead I Micronews

Global 3d Ic And 2 5d Ic Packaging Market Industry Analysis

Global And Chinese 3d Ic And 2 5d Ic Packaging Industry 17 Market Research Report

Insight On The Growth Of 3d Ic And 2 5d Ic Packaging Market Growth With Challenges Standardization By Patilpradnya665 Issuu

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Www Nist Gov Document Bottomspdf

Advanced Semiconductor Packaging Starting To Change Memory Market Landscape Seeking Alpha

Sorting Out Packaging Options

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

2 5d And 3d Designs Semiwiki

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Amkor S Advanced Packaging A Closer Look I Micronews

Highlights Of The Tsmc Technology Symposium 21 Packaging Semiwiki

2 5d Vs

Rolfsted If Dk Hp Ssd S700 Pro 2 5 256gb Sata Iii 3d Nand Internal Ssd 2ap98aa Abl Drives Storage Blank Media Computers Tablets Networking

Rolfsted If Dk Hp Ssd S700 Pro 2 5 256gb Sata Iii 3d Nand Internal Ssd 2ap98aa Abl Drives Storage Blank Media Computers Tablets Networking

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

2d Vs 2 5d Games

2 5d 3d Packaging Applications Indium Corporation

3d Ic 2 5d Ic Packaging Market Size Share Trend And Forcarst To 25 Prof Research

3d Microelectronic Packaging Springerprofessional De

Flip Chip Market By Packaging Technology 3d Ic 2 5d Ic 2d Ic And Trends Research Beam By Rahul Sharma Issuu

Yole Yole Developpement Yole Developpement Yole Development System Plus System Plus Consulting Piezoelectric Bulk Bulk To Thin Film Thin Film Piezo Sensors Actuators Transducers Mobile And Consumer Automotive And Transportation Defense

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

2 5d 3d Packaging Applications Indium Corporation

2 5d 3d Ase Group

Software Handles 2d 2 5d 3d Package Ic System Design

Now You Can Automate Latch Up Verification For 2 5 3d Technologies

Polymer Challenges In Electronic Packaging Overview Polymer Innovation Blog

Left Right Above And Under Intel 3d Packaging Tech Gains Omnidirectionality Hacker News Digest Mdeditor

17 European 3d Summit Making Advanced Packaging Great Again

High End Performance Packaging 3d 2 5d Integration I Micronews

Flexible Multi Sensor Metrology Tool For Advanced Packaging Quote Rfq Price And Buy

Logistics Cost For 2 5d 3d Sic Download Scientific Diagram

Toward 2 5 3d Packaging Enablement Through Copper Pillar

3d Ic And 2 5d Ic Packaging Global Market Trajectory Analytics

Yole Developpement 3d Packaging Free Webcast On May 27 Yole Dev System Plus Consulting Join Forces To Share Their Expertise On The 2 5d 3d Packaging We Will Also

0 件のコメント:

コメントを投稿